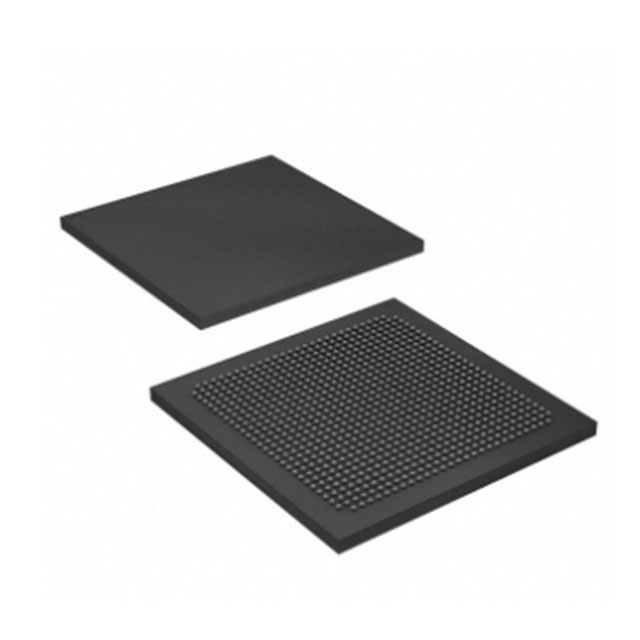

5CEFA5F23I7N Cyclone® VE Field Programmable Gate Array (FPGA) IC 240 5001216 77000 484-BGA

ຄຸນລັກສະນະຂອງຜະລິດຕະພັນ

| ປະເພດ | ຕົວຢ່າງ |

| ປະເພດ | Field Gate Arrays (FPGAs) |

| ຜູ້ຜະລິດ | Intel |

| ຊຸດ | Cyclone® VE |

| ຫໍ່ | ຖາດ |

| ສະຖານະພາບຜະລິດຕະພັນ | ເຄື່ອນໄຫວ |

| DigiKey ແມ່ນໂຄງການ | ບໍ່ມີການຍືນຍັນ |

| ໝາຍເລກ LAB/CLB | 29080 |

| ຈຳນວນຂອງອົງປະກອບ/ຫົວໜ່ວຍ | 77000 |

| ຈໍານວນທັງຫມົດຂອງ RAM bits | 5001216 |

| I/O 數 | 240 |

| ແຮງດັນ - ການສະຫນອງພະລັງງານ | 1.07V ~ 1.13V |

| ປະເພດການຕິດຕັ້ງ | ປະເພດກາວດ້ານ |

| ອຸນຫະພູມປະຕິບັດການ | -40°C ~ 100°C(TJ) |

| ຊຸດ/ທີ່ຢູ່ອາໄສ | 484-BGA |

| ການຫຸ້ມຫໍ່ອົງປະກອບຂອງຜູ້ຂາຍ | 484-FBGA (23x23) |

| ໝາຍເລກຜະລິດຕະພັນ | 5CEFA5 |

ແນະນຳຜະລິດຕະພັນ

ອຸປະກອນ Cyclone® V ຖືກອອກແບບມາພ້ອມໆກັນເພື່ອຮອງຮັບການຫົດຕົວຂອງການໃຊ້ພະລັງງານ, ຄ່າໃຊ້ຈ່າຍ, ແລະເວລາຕໍ່ຕະຫຼາດ;ແລະຄວາມຕ້ອງການແບນວິດທີ່ເພີ່ມຂຶ້ນສໍາລັບຄໍາຮ້ອງສະຫມັກທີ່ມີປະລິມານສູງແລະຄ່າໃຊ້ຈ່າຍທີ່ລະອຽດອ່ອນ.ປັບປຸງດ້ວຍຕົວຮັບສັນຍານແບບປະສົມປະສານ ແລະເຄື່ອງຄວບຄຸມຄວາມຈຳແຂງ, ອຸປະກອນ Cyclone V ເໝາະສຳລັບແອັບພລິເຄຊັນໃນອຸດສາຫະກຳ, ໄຮ້ສາຍ ແລະສາຍສາຍ, ການທະຫານ ແລະຕະຫຼາດລົດຍົນ.

ຄຸນສົມບັດຜະລິດຕະພັນ

ເຕັກໂນໂລຊີ

- ເທັກໂນໂລຍີຂະບວນການພະລັງງານຕໍ່າ 28-nm (28LP) ຂອງ TSMC

- ແຮງດັນຫຼັກ 1.1 V

ການຫຸ້ມຫໍ່

- ການຫຸ້ມຫໍ່ halogen ຕ່ໍາ Wirebond

- ຄວາມຫນາແຫນ້ນຂອງອຸປະກອນຫຼາຍອັນທີ່ມີຮອຍຕີນຂອງຊຸດທີ່ເຂົ້າກັນໄດ້ສໍາລັບການຍ້າຍຖິ່ນຖານລະຫວ່າງຄວາມຫນາແຫນ້ນຂອງອຸປະກອນທີ່ແຕກຕ່າງກັນ.

- ທາງເລືອກທີ່ສອດຄ່ອງກັບ RoHS ແລະນໍາພາ

ຜ້າ FPGA ທີ່ມີປະສິດທິພາບສູງ

- ປັບປຸງ 8-input ALM ດ້ວຍສີ່ທະບຽນ

ຕັນຫນ່ວຍຄວາມຈໍາພາຍໃນ

- ບລັອກໜ່ວຍຄວາມຈຳ M10K—10 ກິໂລບ (Kb) ດ້ວຍລະຫັດການແກ້ໄຂຄວາມຜິດພາດອ່ອນ (ECC)

- Memory logic array block (MLAB) — 640-bit LUTRAM ທີ່ແຈກຢາຍທີ່ທ່ານສາມາດນໍາໃຊ້ໄດ້ເຖິງ 25% ຂອງ ALMs ເປັນຫນ່ວຍຄວາມຈໍາ MLAB

ຝັງບລັອກ Hard IP

- ສະຫນັບສະຫນູນຕົ້ນສະບັບສໍາລັບການເຖິງສາມລະດັບຄວາມແມ່ນຍໍາຂອງການປະມວນຜົນສັນຍານ (ສາມ 9 x 9, ສອງ 18 x 18, ຫຼືຫນຶ່ງຕົວຄູນ 27 x 27) ໃນຕົວປ່ຽນແປງ-precision DSP block ດຽວກັນ.

- 64-bit accumulator ແລະ cascade

- ຝັງຄວາມຊົງຈໍາສໍາປະສິດພາຍໃນ

- Prereadder/subtractor ສໍາລັບການປັບປຸງປະສິດທິພາບ

- DDR3, DDR2, ແລະ LPDDR2 ດ້ວຍການຮອງຮັບ ECC 16 ແລະ 32 ບິດ

- PCI Express* (PCIe*) Gen2 ແລະ Gen1 (x1, x2, ຫຼື x4) hard IP ທີ່ຮອງຮັບຫຼາຍຟັງຊັນ, ຈຸດສິ້ນສຸດ, ແລະພອດຮາກ

ການຕັ້ງຄ່າ

- ການປົກປ້ອງ amper - ການປົກປ້ອງການອອກແບບທີ່ສົມບູນແບບເພື່ອປົກປ້ອງການລົງທຶນ IP ທີ່ມີຄຸນຄ່າຂອງທ່ານ

- ປັບປຸງຄຸນສົມບັດຄວາມປອດໄພໃນການອອກແບບມາດຕະຖານການເຂົ້າລະຫັດຂັ້ນສູງ (AES).

- CVP

- ການຕັ້ງຄ່າແບບໄດນາມິກຂອງ FPGA

- Active serial (AS) x1 ແລະ x4, passive serial (PS), JTAG, ແລະ fast passive parallel (FPP) x8 ແລະ x16 ຕົວເລືອກການຕັ້ງຄ່າ

- ຂັດພາຍໃນ (2)

- ການຕັ້ງຄ່າຄືນໃຫມ່ບາງສ່ວນ (3)

ຂຽນຂໍ້ຄວາມຂອງທ່ານທີ່ນີ້ແລະສົ່ງໃຫ້ພວກເຮົາ