ຊິບອີເລັກໂທຣນິກ ic ສະຫນັບສະຫນູນ BOM ບໍລິການ TPS54560BDDAR ຍີ່ຫໍ້ໃຫມ່ ic chip ອົງປະກອບເອເລັກໂຕຣນິກ

ຄຸນລັກສະນະຂອງຜະລິດຕະພັນ

| ປະເພດ | ລາຍລະອຽດ |

| ປະເພດ | ວົງຈອນລວມ (ICs) |

| Mfr | Texas Instruments |

| ຊຸດ | Eco-Mode™ |

| ຊຸດ | ເທບ ແລະ ມ້ວນ (TR) ແຜ່ນຕັດ (CT) Digi-Reel® |

| SPQ | 2500T&R |

| ສະຖານະພາບຜະລິດຕະພັນ | ເຄື່ອນໄຫວ |

| ຟັງຊັນ | ຂັ້ນຕອນລົງ |

| Output Configuration | ບວກ |

| Topology | Buck, Split Rail |

| ປະເພດຜົນຜະລິດ | ສາມາດປັບໄດ້ |

| ຈໍານວນຜົນໄດ້ຮັບ | 1 |

| ແຮງດັນ - ຂາເຂົ້າ (ນາທີ) | 4.5V |

| ແຮງດັນ - ວັດສະດຸປ້ອນ (ສູງສຸດ) | 60V |

| ແຮງດັນ - ຜົນຜະລິດ (ນາທີ/ຄົງທີ່) | 0.8V |

| ແຮງດັນ - ຜົນຜະລິດ (ສູງສຸດ) | 58.8V |

| ປະຈຸບັນ - ຜົນຜະລິດ | 5A |

| ຄວາມຖີ່ - ສະຫຼັບ | 500kHz |

| Synchronous Rectifier | No |

| ອຸນຫະພູມປະຕິບັດງານ | -40°C ~ 150°C (TJ) |

| ປະເພດການຕິດຕັ້ງ | Surface Mount |

| ການຫຸ້ມຫໍ່ / ກໍລະນີ | 8-PowerSOIC (0.154", ກວ້າງ 3.90mm) |

| ຊຸດອຸປະກອນຜູ້ສະໜອງ | 8-SO PowerPad |

| ໝາຍເລກຜະລິດຕະພັນພື້ນຖານ | TPS54560 |

1.ການຕັ້ງຊື່ IC, ຊຸດຄວາມຮູ້ທົ່ວໄປ ແລະກົດລະບຽບການຕັ້ງຊື່:

ຊ່ວງອຸນຫະພູມ.

C=0°C ຫາ 60°C (ເກຣດການຄ້າ);I=-20°C ຫາ 85°C (ຊັ້ນອຸດສາຫະກໍາ);E=-40°C ຫາ 85°C (ຊັ້ນອຸດສາຫະກໍາຂະຫຍາຍຕົວ);A=-40°C ຫາ 82°C (ຊັ້ນອາວະກາດ);M=-55°C ຫາ 125°C (ຊັ້ນການທະຫານ)

ປະເພດແພັກເກດ.

A-SSOP;B-CERQUAD;C-TO-200, TQFP;D-Ceramic ທອງແດງເທິງ;E-QSOP;F-Ceramic SOP;H- SBGAJ-Ceramic DIP;K-TO-3;L-LCC, M-MQFP;N-ແຄບ DIP;N-DIP;Q PLCC;R - ແຄບ Ceramic DIP (300mil);S - TO-52, T - TO5, TO-99, TO-100;U - TSSOP, uMAX, SOT;W - Wide Small Form Factor (300mil) W-Wide small form factor (300 mil);X-SC-60 (3P, 5P, 6P);Y-ແຄບທອງແດງເທິງ;Z-TO-92, MQUAD;D-Die;/PR-ເສີມພລາສຕິກ;/W-Wafer.

ຈໍານວນຂອງ pins:

a-8;b-10;c-12, 192;d-14;e-16;f-22, 256;g-4;h-4;i -4;H-4;I-28;J-2;K-5, 68;L-40;M-6, 48;ນ 18;O-42;P-20;Q-2, 100;R-3, 843;S-4, 80;T-6, 160;U-60 -6,160;U-60;V-8 (ຮອບ);W-10 (ຮອບ);X-36;Y-8 (ຮອບ);Z-10 (ຮອບ).(ຮອບ).

ຫມາຍເຫດ: ຕົວອັກສອນທໍາອິດຂອງສີ່ຕົວຕໍ່ທ້າຍຂອງຫ້ອງການໂຕ້ຕອບແມ່ນ E, ຊຶ່ງຫມາຍຄວາມວ່າອຸປະກອນມີຫນ້າທີ່ antistatic.

2.ການພັດທະນາເຕັກໂນໂລຢີການຫຸ້ມຫໍ່

ວົງຈອນປະສົມປະສານທີ່ລ້າສະໄຫມທີ່ສຸດແມ່ນໃຊ້ຊຸດຮາບພຽງຂອງເຊລາມິກ, ເຊິ່ງສືບຕໍ່ຖືກນໍາໃຊ້ໂດຍທະຫານເປັນເວລາຫຼາຍປີຍ້ອນຄວາມຫນ້າເຊື່ອຖືແລະຂະຫນາດນ້ອຍ.ການຫຸ້ມຫໍ່ວົງຈອນທາງການຄ້າໄດ້ປ່ຽນໄປເປັນຊຸດຄູ່ໃນແຖວ, ເລີ່ມຕົ້ນດ້ວຍເຊລາມິກແລະຈາກນັ້ນພາດສະຕິກ, ແລະໃນປີ 1980, ການນັບເຂັມຂອງວົງຈອນ VLSI ໄດ້ເກີນຂອບເຂດຈໍາກັດຄໍາຮ້ອງສະຫມັກຂອງຊຸດ DIP, ໃນທີ່ສຸດກໍ່ນໍາໄປສູ່ການເກີດໃຫມ່ຂອງ pin grid arrays ແລະ chip carriers.

ຊຸດຕິດຕັ້ງພື້ນຜິວໄດ້ເກີດຂື້ນໃນຕົ້ນຊຸມປີ 1980 ແລະກາຍເປັນທີ່ນິຍົມໃນສ່ວນຕໍ່ມາຂອງທົດສະວັດນັ້ນ.ມັນໃຊ້ pin pitch ທີ່ລະອຽດກວ່າ ແລະ ມີຮູບຊົງປີກແກວ ຫຼື J-shaped pin.ສໍາລັບຕົວຢ່າງ, ວົງຈອນລວມຂະຫນາດນ້ອຍ -Outline (SOIC), ມີພື້ນທີ່ຫນ້ອຍ 30-50% ແລະມີຄວາມຫນາ 70% ຫນ້ອຍກ່ວາ DIP ທຽບເທົ່າ.ຊຸດນີ້ມີ pins ຮູບ gull-wing-shaped protruding ຈາກທັງສອງດ້ານຍາວແລະ pin pitch ຂອງ 0.05".

ການຫຸ້ມຫໍ່ Small-Outline Integrated Circuit (SOIC) ແລະ PLCC.ໃນຊຸມປີ 1990, ເຖິງແມ່ນວ່າຊຸດ PGA ຍັງຖືກນໍາໃຊ້ເລື້ອຍໆສໍາລັບໂປເຊດເຊີ microprocessors ລະດັບສູງ.ຊຸດ PQFP ແລະຊຸດໂຄງຮ່າງຂະຫນາດນ້ອຍບາງໆ (TSOP) ໄດ້ກາຍເປັນຊຸດປົກກະຕິສໍາລັບອຸປະກອນທີ່ມີຈໍານວນ pin ສູງ.ໄມໂຄຣໂປຣເຊສເຊີລະດັບສູງຂອງ Intel ແລະ AMD ໄດ້ຍ້າຍຈາກແພັກເກັດ PGA (Pine Grid Array) ໄປເປັນແພັກເກັດ Land Grid Array (LGA).

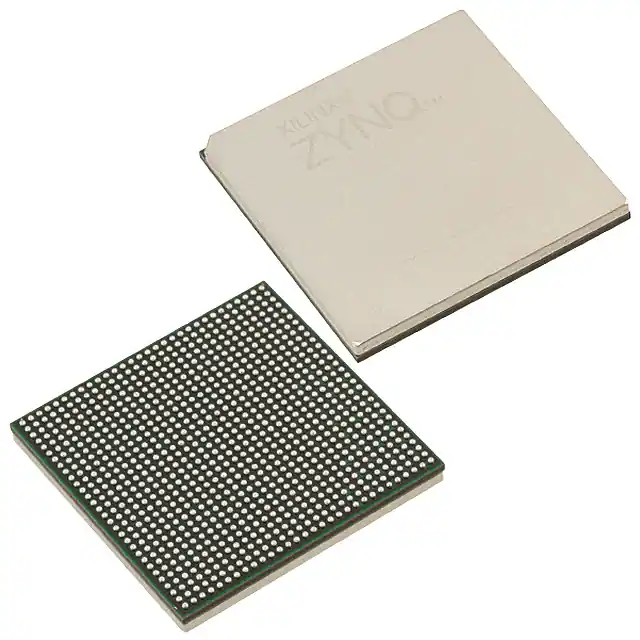

ຊຸດ Ball Grid Array ເລີ່ມປະກົດຕົວໃນຊຸມປີ 1970, ແລະໃນຊຸມປີ 1990 ຊຸດ FCBGA ໄດ້ຖືກພັດທະນາດ້ວຍຈໍານວນ pin ສູງກວ່າຊຸດອື່ນໆ.ໃນຊຸດ FCBGA, ການຕາຍແມ່ນ flipped ຂຶ້ນແລະລົງແລະເຊື່ອມຕໍ່ກັບລູກ solder ໃນຊຸດໂດຍຊັ້ນພື້ນຖານຄ້າຍຄື PCB ແທນທີ່ຈະກ່ວາສາຍ.ໃນຕະຫຼາດມື້ນີ້, ການຫຸ້ມຫໍ່ຍັງເປັນພາກສ່ວນແຍກຕ່າງຫາກຂອງຂະບວນການ, ແລະເຕັກໂນໂລຢີຂອງຊຸດຍັງສາມາດສົ່ງຜົນກະທົບຕໍ່ຄຸນນະພາບແລະຜົນຜະລິດຂອງຜະລິດຕະພັນ.