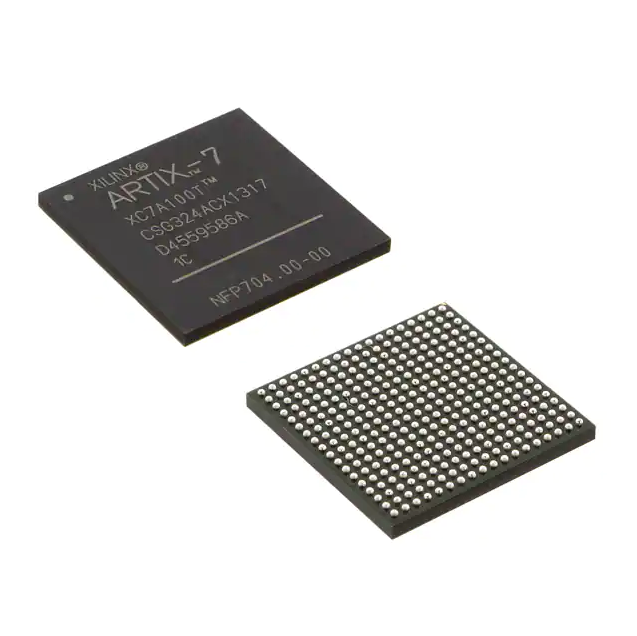

XC5VSX50T-1FFG1136I ວົງຈອນປະສົມປະສານອົງປະກອບເອເລັກໂຕຣນິກຕົ້ນສະບັບແລະຊິບ Ic ໃຫມ່

ຄຸນລັກສະນະຂອງຜະລິດຕະພັນ

| ປະເພດ | ລາຍລະອຽດ | ເລືອກ |

| ປະເພດ | ວົງຈອນລວມ (ICs) |

|

| Mfr | AMD Xilinx |

|

| ຊຸດ | Virtex®-5 SXT |

|

| ຊຸດ | ຖາດ |

|

| ສະຖານະພາບຜະລິດຕະພັນ | ເຄື່ອນໄຫວ |

|

| ຈຳນວນຫ້ອງທົດລອງ/CLBs | 4080 |

|

| ຈໍານວນຂອງອົງປະກອບ Logic/Cells | 52224 |

|

| ຈໍານວນ RAM ທັງຫມົດ | 4866048 |

|

| ຈໍານວນ I/O | 480 |

|

| ແຮງດັນ - ການສະຫນອງ | 0.95V ~ 1.05V |

|

| ປະເພດການຕິດຕັ້ງ | Surface Mount |

|

| ອຸນຫະພູມປະຕິບັດການ | -40°C ~ 100°C (TJ) |

|

| ການຫຸ້ມຫໍ່ / ກໍລະນີ | 1136-BBGA, FCBGA |

|

| ຊຸດອຸປະກອນຜູ້ສະໜອງ | 1136-FCBGA (35×35) |

|

| ໝາຍເລກຜະລິດຕະພັນພື້ນຖານ | XC5VSX50 |

|

ລາຍງານຂໍ້ມູນຜະລິດຕະພັນຜິດພາດ

ເບິ່ງຄ້າຍຄືກັນ

ເອກະສານ ແລະສື່

| ປະເພດຊັບພະຍາກອນ | ລິ້ງ |

| ເອກະສານຂໍ້ມູນ | Virtex-5 Family Overview |

| ຂໍ້ມູນສິ່ງແວດລ້ອມ | Xiliinx ໃບຢັ້ງຢືນ RoHS |

| ການອອກແບບ / ຂໍ້ມູນຈໍາເພາະ PCN | ແຈ້ງການຫ້າມນຳເຮືອຂ້າມຟາກໃນວັນທີ 31/10/2016 |

ການຈັດປະເພດສິ່ງແວດລ້ອມ ແລະສົ່ງອອກ

| ຄຸນສົມບັດ | ລາຍລະອຽດ |

| ສະຖານະ RoHS | ສອດຄ່ອງ ROHS3 |

| ລະດັບຄວາມອ່ອນໄຫວຄວາມຊຸ່ມຊື່ນ (MSL) | 4 (72 ຊົ່ວໂມງ) |

| ສະຖານະການເຂົ້າເຖິງ | ເຂົ້າເຖິງບໍ່ໄດ້ຮັບຜົນກະທົບ |

| ECCN | 3A001A7A |

| HTSUS | 8542.39.0001 |

array gate-programmable ພາກສະຫນາມ

ກarray gate-programmable field-programmable(FPGA) ເປັນວົງຈອນລວມອອກແບບມາເພື່ອກຳນົດຄ່າໂດຍລູກຄ້າ ຫຼືຜູ້ອອກແບບຫຼັງຈາກການຜະລິດ – ສະນັ້ນ ຄຳສັບfield-programmable.ການຕັ້ງຄ່າ FPGA ໂດຍທົ່ວໄປແມ່ນຖືກກໍານົດໂດຍໃຊ້ aພາສາຄໍາອະທິບາຍຮາດແວ(HDL), ຄ້າຍຄືກັນກັບທີ່ໃຊ້ສໍາລັບການວົງຈອນລວມຂອງແອັບພລິເຄຊັນສະເພາະ(ASIC).ແຜນວາດວົງຈອນໄດ້ຖືກນໍາໃຊ້ໃນເມື່ອກ່ອນເພື່ອກໍານົດການຕັ້ງຄ່າ, ແຕ່ນີ້ແມ່ນຫາຍາກເພີ່ມຂຶ້ນເນື່ອງຈາກການມາເຖິງຂອງອັດຕະໂນມັດການອອກແບບເອເລັກໂຕຣນິກເຄື່ອງມື.

FPGAs ມີ array ຂອງສາມາດຕັ້ງໂປຣແກຣມໄດ້ ຕັນຕາມເຫດຜົນ, ແລະລໍາດັບຊັ້ນຂອງການເຊື່ອມຕໍ່ກັນຄືນໃຫມ່ທີ່ອະນຸຍາດໃຫ້ບລັອກສາມາດເຊື່ອມຕໍ່ກັນໄດ້.ຕັນຕາມເຫດຜົນສາມາດຖືກຕັ້ງຄ່າເພື່ອປະຕິບັດສະລັບສັບຊ້ອນຫນ້າທີ່ປະສົມປະສານ, ຫຼືປະຕິບັດເປັນງ່າຍດາຍປະຕູຮົ້ວຕາມເຫດຜົນມັກແລະແລະXOR.ໃນ FPGAs ສ່ວນໃຫຍ່, ຕັນທາງຕັນຍັງປະກອບມີອົງປະກອບຄວາມຊົງຈໍາ, ຊຶ່ງອາດຈະງ່າຍດາຍflip-flopsຫຼືຄວາມຊົງຈໍາທີ່ສົມບູນກວ່າ.[1]FPGAs ຈໍານວນຫຼາຍສາມາດ reprogrammed ເພື່ອປະຕິບັດທີ່ແຕກຕ່າງກັນຟັງຊັນຕາມເຫດຜົນ, ອະນຸຍາດໃຫ້ມີຄວາມຍືດຫຍຸ່ນຄອມພິວເຕີທີ່ສາມາດປັບແຕ່ງໄດ້ດັ່ງທີ່ໄດ້ປະຕິບັດໃນຊອບແວຄອມພິວເຕີ.

FPGAs ມີບົດບາດທີ່ໂດດເດັ່ນໃນລະບົບຝັງການພັດທະນາເນື່ອງຈາກຄວາມສາມາດໃນການເລີ່ມຕົ້ນການພັດທະນາຊອບແວລະບົບພ້ອມໆກັນກັບຮາດແວ, ເປີດໃຊ້ການຈໍາລອງການປະຕິບັດລະບົບໃນຊ່ວງຕົ້ນໆຂອງການພັດທະນາ, ແລະອະນຸຍາດໃຫ້ມີການທົດລອງລະບົບຕ່າງໆແລະການອອກແບບຄືນໃຫມ່ກ່ອນທີ່ຈະສໍາເລັດໂຄງສ້າງລະບົບ.[2]

ປະຫວັດສາດ[ແກ້ໄຂ]

ອຸດສາຫະກໍາ FPGA sprouted ຈາກໜ່ວຍຄວາມຈຳແບບອ່ານເທົ່ານັ້ນທີ່ສາມາດຂຽນໂປຣແກຣມໄດ້(PROM) ແລະອຸປະກອນຕາມເຫດຜົນຂອງໂປຣແກຣມ(PLDs).PROMs ແລະ PLDs ທັງສອງມີທາງເລືອກໃນການດໍາເນີນໂຄງການເປັນ batches ໃນໂຮງງານຫຼືໃນພາກສະຫນາມ (field-programmable).[3]

Alteraໄດ້ຖືກສ້າງຕັ້ງຂຶ້ນໃນປີ 1983 ແລະໄດ້ສົ່ງອຸປະກອນຕາມເຫດຜົນ reprogrammable ທໍາອິດຂອງອຸດສາຫະກໍາໃນປີ 1984 - EP300 - ເຊິ່ງມີລັກສະນະເປັນປ່ອງຢ້ຽມ quartz ໃນຊຸດທີ່ອະນຸຍາດໃຫ້ຜູ້ໃຊ້ສາມາດສ່ອງແສງໂຄມໄຟ ultra-violet ເທິງເຄື່ອງຕາຍເພື່ອລົບລ້າງ.EPROMຈຸລັງທີ່ຖືການຕັ້ງຄ່າອຸປະກອນ.[4]

Xilinxຜະລິດເປັນພາກສະຫນາມ-programmable ທາງດ້ານການຄ້າຄັ້ງທໍາອິດgate arrayໃນປີ 1985[3]- XC2064.[5]XC2064 ມີປະຕູທີ່ສາມາດຂຽນໂປຣແກຣມໄດ້ ແລະສາມາດເຊື່ອມຕໍ່ກັນໄດ້ລະຫວ່າງປະຕູ, ການເລີ່ມຕົ້ນຂອງເທັກໂນໂລຍີໃໝ່ ແລະຕະຫຼາດ.[6]XC2064 ມີ 64 ຕັນ logic ທີ່ສາມາດຕັ້ງຄ່າໄດ້ (CLBs), ມີສອງສາມ input.ຕາຕະລາງຊອກຫາ(LUTs).[7]

ໃນປີ 1987, ໄດ້ສູນກາງການສູ້ຮົບພື້ນຜິວເຮືອໄດ້ໃຫ້ທຶນແກ່ການທົດລອງທີ່ສະເໜີໂດຍ Steve Casselman ເພື່ອພັດທະນາຄອມພິວເຕີທີ່ຈະປະຕິບັດ 600,000 reprogrammable gates.Casselman ປະສົບຜົນສໍາເລັດແລະສິດທິບັດທີ່ກ່ຽວຂ້ອງກັບລະບົບໄດ້ຖືກອອກໃນປີ 1992.[3]

Altera ແລະ Xilinx ສືບຕໍ່ບໍ່ທ້າທາຍແລະຂະຫຍາຍຕົວຢ່າງໄວວາຈາກ 1985 ຫາກາງຊຸມປີ 1990 ເມື່ອຄູ່ແຂ່ງໄດ້ເຕີບໃຫຍ່ຂຶ້ນ, ທໍາລາຍສ່ວນທີ່ສໍາຄັນຂອງສ່ວນແບ່ງຕະຫຼາດຂອງພວກເຂົາ.ໃນປີ 1993, Actel (ປະຈຸບັນໄມໂຄຣເຊມິ) ໄດ້ໃຫ້ບໍລິການປະມານ 18 ເປີເຊັນຂອງຕະຫຼາດ.[6]

ຊຸມປີ 1990 ແມ່ນໄລຍະເວລາຂອງການຂະຫຍາຍຕົວຢ່າງໄວວາສໍາລັບ FPGAs, ທັງໃນຄວາມຊັບຊ້ອນຂອງວົງຈອນແລະປະລິມານການຜະລິດ.ໃນຕົ້ນຊຸມປີ 1990, FPGAs ຖືກນໍາໃຊ້ຕົ້ນຕໍໃນໂທລະຄົມມະນາຄົມແລະເຄືອຂ່າຍ.ໃນຕອນທ້າຍຂອງທົດສະວັດ, FPGAs ໄດ້ພົບເຫັນວິທີການຂອງເຂົາເຈົ້າເຂົ້າໄປໃນຜູ້ບໍລິໂພກ, ລົດຍົນ, ແລະຄໍາຮ້ອງສະຫມັກອຸດສາຫະກໍາ.[8]

ໃນປີ 2013, Altera (31 ເປີເຊັນ), Actel (10 ເປີເຊັນ) ແລະ Xilinx (36 ເປີເຊັນ) ຮ່ວມກັນເປັນຕົວແທນປະມານ 77 ເປີເຊັນຂອງຕະຫຼາດ FPGA.[9]

ບໍລິສັດເຊັ່ນ Microsoft ໄດ້ເລີ່ມໃຊ້ FPGAs ເພື່ອເລັ່ງລະບົບທີ່ມີປະສິດຕິພາບສູງ, ຄອມພິວເຕີທີ່ເຂັ້ມຂຸ້ນ (ເຊັ່ນ:ສູນຂໍ້ມູນທີ່ດໍາເນີນການຂອງເຂົາເຈົ້າເຄື່ອງຈັກຊອກຫາ Bing), ເນື່ອງຈາກປະສິດທິພາບຕໍ່ວັດປະໂຫຍດ FPGAs ສົ່ງ.[10]Microsoft ເລີ່ມໃຊ້ FPGAs ເພື່ອເລັ່ງBing ໃນປີ 2014, ແລະໃນປີ 2018 ໄດ້ເລີ່ມນຳໃຊ້ FPGAs ໃນທົ່ວບ່ອນເຮັດວຽກຂອງສູນຂໍ້ມູນອື່ນໆສຳລັບພວກເຂົາ.Azure ຄອມພິວເຕີ້ຟັງເວທີ.[11]

ໄລຍະເວລາຕໍ່ໄປນີ້ຊີ້ໃຫ້ເຫັນຄວາມຄືບຫນ້າໃນລັກສະນະທີ່ແຕກຕ່າງກັນຂອງການອອກແບບ FPGA:

ປະຕູ

- 1987: 9,000 ປະຕູ, Xilinx[6]

- 1992: 600,000, ກົມສົງຄາມພື້ນຜິວຂອງກອງທັບເຮືອ[3]

- ຕົ້ນປີ 2000: ລ້ານ[8]

- 2013: 50 ລ້ານ, Xilinx[12]

ຂະຫນາດຕະຫຼາດ

- 1985: FPGA ການຄ້າຄັ້ງທໍາອິດ: Xilinx XC2064[5][6]

- ປີ 1987: 14 ລ້ານໂດລາ[6]

- ຄ.1993: > 385 ລ້ານໂດລາສະຫະລັດ[6][ການຢັ້ງຢືນລົ້ມເຫລວ]

- 2005: 1.9 ຕື້ໂດລາ[13]

- ປີ 2010 ຄາດຄະເນ: 2,75 ຕື້ໂດລາ[13]

- ປີ 2013: 5,4 ຕື້ໂດລາ[14]

- ຄາດວ່າປີ 2020: 9,8 ຕື້ໂດລາ[14]

ການອອກແບບເລີ່ມຕົ້ນ

ກການເລີ່ມຕົ້ນການອອກແບບແມ່ນການອອກແບບທີ່ກໍາຫນົດເອງໃຫມ່ສໍາລັບການປະຕິບັດໃນ FPGA.

ອອກແບບ[ແກ້ໄຂ]

FPGAs ໃນປະຈຸບັນມີຊັບພະຍາກອນຂະຫນາດໃຫຍ່ຂອງປະຕູຮົ້ວຕາມເຫດຜົນແລະຕັນ RAM ເພື່ອປະຕິບັດການຄິດໄລ່ດິຈິຕອນທີ່ສັບສົນ.ຍ້ອນວ່າການອອກແບບ FPGA ນຳໃຊ້ອັດຕາ I/O ທີ່ໄວຫຼາຍ ແລະຂໍ້ມູນສອງທິດທາງລົດເມ, ມັນກາຍເປັນສິ່ງທ້າທາຍທີ່ຈະກວດສອບການກໍານົດເວລາທີ່ຖືກຕ້ອງຂອງຂໍ້ມູນທີ່ຖືກຕ້ອງພາຍໃນເວລາຕັ້ງຄ່າແລະເວລາຖື.

ການວາງແຜນຊັ້ນເຮັດໃຫ້ການຈັດສັນຊັບພະຍາກອນພາຍໃນ FPGAs ເພື່ອຕອບສະຫນອງຂໍ້ຈໍາກັດເວລາເຫຼົ່ານີ້.FPGAs ສາມາດຖືກນໍາໃຊ້ເພື່ອປະຕິບັດຫນ້າທີ່ມີເຫດຜົນໃດກໍ່ຕາມASICສາມາດປະຕິບັດ.ຄວາມສາມາດໃນການປັບປຸງການເຮັດວຽກຫຼັງຈາກການຂົນສົ່ງ,ການຕັ້ງຄ່າຄືນໃຫມ່ບາງສ່ວນບາງສ່ວນຂອງການອອກແບບ[17]ແລະຄ່າໃຊ້ຈ່າຍດ້ານວິສະວະກໍາທີ່ບໍ່ເກີດຂຶ້ນຊໍ້າຕ່ໍາທີ່ກ່ຽວຂ້ອງກັບການອອກແບບ ASIC (ເຖິງແມ່ນວ່າຄ່າໃຊ້ຈ່າຍຕໍ່ຫນ່ວຍທີ່ສູງກວ່າໂດຍທົ່ວໄປ), ສະເຫນີຂໍ້ດີສໍາລັບຄໍາຮ້ອງສະຫມັກຈໍານວນຫຼາຍ.[1]

ບາງ FPGAs ມີລັກສະນະການປຽບທຽບນອກເຫນືອຈາກຫນ້າທີ່ດິຈິຕອນ.ລັກສະນະການປຽບທຽບທົ່ວໄປທີ່ສຸດແມ່ນໂຄງການອັດຕາການລ້າໃນແຕ່ລະ pin ຜົນຜະລິດ, ອະນຸຍາດໃຫ້ວິສະວະກອນກໍານົດອັດຕາຕ່ໍາສຸດ pins loaded lightly ຖ້າບໍ່ດັ່ງນັ້ນແຫວນຫຼືຄູ່ຍອມຮັບບໍ່ໄດ້, ແລະເພື່ອກໍານົດອັດຕາທີ່ສູງຂຶ້ນໃນ pins ໂຫຼດຫຼາຍໃນຊ່ອງທາງຄວາມໄວສູງທີ່ຖ້າບໍ່ດັ່ງນັ້ນຈະແລ່ນຊ້າເກີນໄປ.[18][19]ທົ່ວໄປແມ່ນ quartz-oscillators ໄປເຊຍກັນ, on-chip resistance-capacitance oscillators, ແລະloops ລັອກໄລຍະດ້ວຍການຝັງoscillators ຄວບຄຸມແຮງດັນໃຊ້ສໍາລັບການຜະລິດໂມງແລະການຄຸ້ມຄອງເຊັ່ນດຽວກັນກັບສໍາລັບ serializer-deserializer ຄວາມໄວສູງ (SERDES) ສົ່ງໂມງແລະການຟື້ນຕົວໂມງຮັບ.ຂ້ອນຂ້າງທົ່ວໄປແມ່ນຄວາມແຕກຕ່າງຜູ້ປຽບທຽບໃນ pins input ອອກແບບມາເພື່ອເຊື່ອມຕໍ່ກັບສັນຍານຄວາມແຕກຕ່າງຊ່ອງ.ສອງສາມ "ສັນຍານປະສົມFPGAs” ມີອຸປະກອນເສີມປະສົມປະສານຕົວປ່ຽນອະນາລັອກເປັນດິຈິຕອນ(ADCs) ແລະຕົວປ່ຽນດິຈິຕອນເປັນອະນາລັອກ(DACs) ທີ່ມີຕັນປັບສັນຍານອະນາລັອກອະນຸຍາດໃຫ້ເຂົາເຈົ້າດໍາເນີນການເປັນsystem-on-a-chip(SoC).[20]ອຸປະກອນດັ່ງກ່າວມົວເສັ້ນລະຫວ່າງ FPGA, ເຊິ່ງນໍາເອົາດິຈິຕອນແລະສູນຢູ່ໃນຜ້າການເຊື່ອມຕໍ່ກັນຂອງຕົນທີ່ຕັ້ງໂຄງການ, ແລະarray ອະນາລັອກທີ່ຕັ້ງໂປຣແກຣມໄດ້ພາກສະຫນາມ(FPAA), ເຊິ່ງມີຄ່າອະນາລັອກຢູ່ໃນຜ້າທີ່ສາມາດເຊື່ອມຕໍ່ກັນໄດ້ພາຍໃນໂຄງການ.