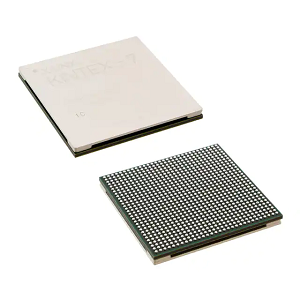

XC7K420T-2FFG901I – ວົງຈອນປະສົມປະສານ, ຝັງ, ອາເຣ Gate Programmable ພາກສະໜາມ

ຄຸນລັກສະນະຂອງຜະລິດຕະພັນ

| ປະເພດ | ຕົວຢ່າງ |

| ປະເພດ | ວົງຈອນລວມ (ICs)ຝັງ Field Gate Arrays (FPGAs) |

| ຜູ້ຜະລິດ | AMD |

| ຊຸດ | Kintex®-7 |

| ຫໍ່ | ຖາດ |

| ສະຖານະພາບຜະລິດຕະພັນ | ເຄື່ອນໄຫວ |

| DigiKey ແມ່ນໂຄງການ | ບໍ່ມີການຍືນຍັນ |

| ໝາຍເລກ LAB/CLB | 32575 |

| ຈຳນວນຂອງອົງປະກອບ/ຫົວໜ່ວຍ | 416960 |

| ຈໍານວນທັງຫມົດຂອງ RAM bits | 30781440 |

| ຈຳນວນ I/Os | 380 |

| ແຮງດັນ - ການສະຫນອງພະລັງງານ | 0.97V ~ 1.03V |

| ປະເພດການຕິດຕັ້ງ | ປະເພດກາວດ້ານ |

| ອຸນຫະພູມປະຕິບັດການ | -40°C ~ 100°C (TJ) |

| ຊຸດ/ທີ່ຢູ່ອາໄສ | 900-BBGA,FCBGA |

| ການຫຸ້ມຫໍ່ອົງປະກອບຂອງຜູ້ຂາຍ | 901-FCBGA (31x31) |

| ໝາຍເລກຜະລິດຕະພັນ | XC7K420 |

| ປະເພດ | ຕົວຢ່າງ |

| ປະເພດ | ວົງຈອນລວມ (ICs)ຝັງ |

| ຜູ້ຜະລິດ | AMD |

| ຊຸດ | Kintex®-7 |

| ຫໍ່ | ຖາດ |

| ສະຖານະພາບຜະລິດຕະພັນ | ເຄື່ອນໄຫວ |

| DigiKey ແມ່ນໂຄງການ | ບໍ່ມີການຍືນຍັນ |

| ໝາຍເລກ LAB/CLB | 32575 |

| ຈຳນວນຂອງອົງປະກອບ/ຫົວໜ່ວຍ | 416960 |

| ຈໍານວນທັງຫມົດຂອງ RAM bits | 30781440 |

| ຈຳນວນ I/Os | 380 |

| ແຮງດັນ - ການສະຫນອງພະລັງງານ | 0.97V ~ 1.03V |

| ປະເພດການຕິດຕັ້ງ | ປະເພດກາວດ້ານ |

| ອຸນຫະພູມປະຕິບັດການ | -40°C ~ 100°C (TJ) |

| ຊຸດ/ທີ່ຢູ່ອາໄສ | 900-BBGA,FCBGA |

| ການຫຸ້ມຫໍ່ອົງປະກອບຂອງຜູ້ຂາຍ | 901-FCBGA (31x31) |

| ໝາຍເລກຜະລິດຕະພັນ | XC7K420 |

FPGAs

ຂໍ້ດີ

ຂໍ້ດີຂອງ FPGAs ມີດັ່ງນີ້:

(1) FPGAs ປະກອບດ້ວຍຊັບພະຍາກອນຂອງຮາດແວເຊັ່ນ: ຈຸລັງຕາມເຫດຜົນ, RAM, ຕົວຄູນ, ແລະອື່ນໆ. ໂດຍການຈັດລຽງຊັບພະຍາກອນຮາດແວເຫຼົ່ານີ້ຢ່າງສົມເຫດສົມຜົນ, ວົງຈອນຮາດແວເຊັ່ນຕົວຄູນ, ທະບຽນ, ເຄື່ອງກໍາເນີດທີ່ຢູ່, ແລະອື່ນໆສາມາດປະຕິບັດໄດ້.

(2) FPGAs ສາມາດອອກແບບໄດ້ໂດຍການໃຊ້ແຜນວາດຕັນຫຼື Verilog HDL, ຈາກວົງຈອນປະຕູງ່າຍດາຍໄປຫາວົງຈອນ FIR ຫຼື FFT.

(3) FPGAs ສາມາດ reprogrammed infinitely, loading a new design solution in just a few hundred milliseconds, using reconfiguration to reduce hardware overhead.

(4) ຄວາມຖີ່ຂອງການດໍາເນີນງານຂອງ FPGA ຖືກກໍານົດໂດຍຊິບ FPGA ເຊັ່ນດຽວກັນກັບການອອກແບບ, ແລະສາມາດດັດແປງຫຼືປ່ຽນຊິບໄວເພື່ອຕອບສະຫນອງຄວາມຕ້ອງການທີ່ຕ້ອງການບາງຢ່າງ (ເຖິງແມ່ນວ່າ, ແນ່ນອນ, ຄວາມຖີ່ຂອງການດໍາເນີນງານແມ່ນບໍ່ຈໍາກັດແລະສາມາດ. ເພີ່ມຂຶ້ນ, ແຕ່ຖືກຄຸ້ມຄອງໂດຍຂະບວນການ IC ໃນປະຈຸບັນແລະປັດໃຈອື່ນໆ).

ຂໍ້ເສຍ

ຂໍ້ເສຍຂອງ FPGAs ມີດັ່ງນີ້:

(1) FPGAs ອີງໃສ່ການປະຕິບັດຮາດແວສໍາລັບຫນ້າທີ່ທັງຫມົດແລະບໍ່ສາມາດປະຕິບັດການດໍາເນີນການເຊັ່ນ: ການໂດດຕາມເງື່ອນໄຂຂອງສາຂາ.

(2) FPGAs ພຽງແຕ່ສາມາດປະຕິບັດການດໍາເນີນງານທີ່ມີຈຸດຄົງທີ່.

ສະຫຼຸບ: FPGAs ອີງໃສ່ຮາດແວເພື່ອປະຕິບັດຫນ້າທີ່ທັງຫມົດແລະສາມາດປຽບທຽບກັບຊິບທີ່ອຸທິດຕົນໃນແງ່ຂອງຄວາມໄວ, ແຕ່ມີຊ່ອງຫວ່າງໃຫຍ່ໃນຄວາມຍືດຫຍຸ່ນໃນການອອກແບບເມື່ອທຽບກັບໂປເຊດເຊີຈຸດປະສົງທົ່ວໄປ.

ອອກແບບພາສາ ແລະເວທີ

ອຸປະກອນຕາມເຫດຜົນຂອງໂຄງການແມ່ນບັນທຸກຮາດແວທີ່ concretize ຫນ້າທີ່ສ້າງຕັ້ງຂຶ້ນແລະສະເພາະດ້ານວິຊາການຂອງຄໍາຮ້ອງສະຫມັກເອເລັກໂຕຣນິກໂດຍຜ່ານເຕັກໂນໂລຊີ EDA.FPGAs, ເປັນຫນຶ່ງໃນອຸປະກອນຕົ້ນຕໍທີ່ປະຕິບັດເສັ້ນທາງນີ້, ແມ່ນອີງໃສ່ຜູ້ໃຊ້ໂດຍກົງ, ມີຄວາມຍືດຫຍຸ່ນແລະຫລາກຫລາຍ, ການນໍາໃຊ້ງ່າຍ, ແລະໄວໃນການທົດສອບແລະປະຕິບັດໃນຮາດແວ.

ພາສາຄໍາອະທິບາຍຮາດແວ (HDL) ແມ່ນພາສາທີ່ໃຊ້ໃນການອອກແບບລະບົບ logic ດິຈິຕອລແລະອະທິບາຍວົງຈອນດິຈິຕອນ, ພາສາຕົ້ນຕໍທີ່ໃຊ້ທົ່ວໄປແມ່ນ VHDL, Verilog HDL, System Verilog ແລະລະບົບ C.

ໃນຖານະເປັນພາສາການອະທິບາຍຮາດແວໄດ້ຕະຫຼອດຄວາມໄວສູງຫຼາຍ Integrated Circuit Hardware Description Language (VHDL) ມີລັກສະນະຂອງການເປັນເອກະລາດຂອງວົງຈອນຮາດແວສະເພາະໃດຫນຶ່ງແລະເປັນເອກະລາດຂອງເວທີການອອກແບບ, ມີຄວາມໄດ້ປຽບຂອງຄວາມສາມາດບັນຍາຍລະດັບຄວາມກວ້າງຂວາງ, ບໍ່. ຂຶ້ນກັບອຸປະກອນສະເພາະ, ແລະຄວາມສາມາດໃນການອະທິບາຍການອອກແບບຂອງເຫດຜົນການຄວບຄຸມທີ່ຊັບຊ້ອນໃນລະຫັດທີ່ເຄັ່ງຄັດແລະຊັດເຈນ, ແລະອື່ນໆ.ມັນໄດ້ຮັບການສະຫນັບສະຫນູນຈາກບໍລິສັດ EDA ຈໍານວນຫຼາຍແລະໄດ້ຖືກນໍາໃຊ້ຢ່າງກວ້າງຂວາງໃນການອອກແບບເອເລັກໂຕຣນິກ.ໃຊ້ຢ່າງກວ້າງຂວາງ.

VHDL ເປັນພາສາລະດັບສູງສໍາລັບການອອກແບບວົງຈອນ, ແລະເມື່ອປຽບທຽບກັບພາສາຄໍາອະທິບາຍຮາດແວອື່ນໆ, ມັນມີລັກສະນະຂອງພາສາທີ່ງ່າຍດາຍ, ຄວາມຍືດຫຍຸ່ນແລະເປັນເອກະລາດຈາກການອອກແບບອຸປະກອນ, ເຮັດໃຫ້ມັນເປັນພາສາຄໍາອະທິບາຍຮາດແວທົ່ວໄປສໍາລັບເຕັກໂນໂລຊີ EDA ແລະເຮັດໃຫ້ເຕັກໂນໂລຊີ EDA ຫຼາຍ. ສາມາດເຂົ້າເຖິງຜູ້ອອກແບບ.

Verilog HDL ເປັນພາສາຄໍາອະທິບາຍຮາດແວທີ່ໃຊ້ກັນຢ່າງກວ້າງຂວາງທີ່ສາມາດຖືກນໍາໃຊ້ໃນຫຼາຍຂັ້ນຕອນຂອງຂະບວນການອອກແບບຮາດແວ, ລວມທັງການສ້າງແບບຈໍາລອງ, ການສັງເຄາະແລະການຈໍາລອງ.

Verilog HDL ຂໍ້ດີ: ຄ້າຍຄືກັນກັບ C, ງ່າຍຕໍ່ການຮຽນຮູ້ແລະມີຄວາມຍືດຫຍຸ່ນ.ກໍລະນີທີ່ລະອຽດອ່ອນ.ຂໍ້ໄດ້ປຽບໃນການຂຽນການກະຕຸ້ນແລະການສ້າງແບບຈໍາລອງ.ຂໍ້ເສຍ: ຄວາມຜິດພາດຫຼາຍບໍ່ສາມາດກວດພົບໃນເວລາລວບລວມ.

VHDL Pros: syntax ເຂັ້ມງວດ, ລໍາດັບຊັ້ນທີ່ຊັດເຈນ.ຂໍ້ເສຍ: ໃຊ້ເວລາຄຸ້ນເຄີຍດົນນານ, ບໍ່ມີຄວາມຄ່ອງຕົວພຽງພໍ.

ຊອບແວ Quartus_II ແມ່ນສະພາບແວດລ້ອມການອອກແບບຫຼາຍເວທີທີ່ສົມບູນທີ່ພັດທະນາໂດຍ Altera, ເຊິ່ງສາມາດຕອບສະຫນອງຄວາມຕ້ອງການຂອງການອອກແບບຂອງ FPGAs ແລະ CPLDs ຕ່າງໆ, ແລະເປັນສະພາບແວດລ້ອມທີ່ສົມບູນແບບສໍາລັບການອອກແບບລະບົບການຂຽນໂປຼແກຼມເທິງຊິບ.

Vivado Design Suite, ສະພາບແວດລ້ອມການອອກແບບປະສົມປະສານທີ່ປ່ອຍອອກມາໂດຍຜູ້ຂາຍ FPGA Xilinx ໃນປີ 2012. ມັນປະກອບມີສະພາບແວດລ້ອມການອອກແບບທີ່ປະສົມປະສານສູງ ແລະເຄື່ອງມືການຜະລິດໃໝ່ຈາກລະບົບເຖິງລະດັບ IC, ທັງໝົດສ້າງຂຶ້ນໃນແບບຂໍ້ມູນທີ່ສາມາດຂະຫຍາຍໄດ້ຮ່ວມກັນ ແລະສະພາບແວດລ້ອມດີບັກທົ່ວໄປ.Xilinx Vivado Design Suite ສະໜອງຫຼັກ FIFO IP ທີ່ສາມາດໃຊ້ກັບການອອກແບບໄດ້ງ່າຍ.